# (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 109037260 A (43)申请公布日 2018.12.18

(21)申请号 201710431792.1

(22)申请日 2017.06.09

(71)申请人 美商晶典有限公司 地址 美国得克萨斯州

(72)发明人 黄振潮 王协友 吕旻晃 王利明

(74)专利代理机构 上海专利商标事务所有限公司 31100

代理人 徐伟

(51) Int.CI.

H01L 27/15(2006.01)

权利要求书2页 说明书11页 附图19页

#### (54)发明名称

微发光二极管显示模块及其制造方法

#### (57)摘要

本发明关于一种微发光二极管显示模块及 其制造方法。该微发光二极管显示模块,包括一 驱动芯片区块、一发光二极管区块、一电路板及 一色层。该驱动芯片区块具有多个像素电极。该 发光二极管区块设于该驱动芯片区块,且具有二 半导体层、及多个沟槽,该二半导体层其中一者 电性连接该等像素电极、另一者连接一透光导电 层。该等沟槽界定出多个呈矩阵排列的微发光二 极管像素,各该沟槽至少穿透该发光层、及一该 半导体层,各该微发光二极管像素对应一该像素 电极。该电路板电性连接该驱动芯片区块,该色 层设于该透光导电层。

1.一种微发光二极管显示模块的制造方法,该制造方法包括以下步骤:

制备一发光二极管晶圆及一驱动电路晶圆,其中该发光二极管晶圆的部分区域界定为一发光二极管区块,该驱动电路晶圆的一芯片大小的区域界定为一驱动芯片区块,其中该发光二极管区块具有一第一半导体层、一发光层、及一第二半导体层,该发光层设于该第一半导体层及该第二半导体层之间,该第一半导体层连接一基材,该第一及该第二半导体层其中一者系为N型半导体层、另一者系为P型半导体层;

接合该发光二极管区块与该驱动芯片区块,其中该第二半导体层与该驱动芯片区块的多个像素电极电性连接;

去除该基材:

蚀刻该发光二极管区块,而形成交错排列的多个沟槽,其中该等沟槽界定出呈矩阵排列的多个微发光二极管像素,各该微发光二极管像素对应一该像素电极;

设置一透光导电层于该第一半导体层上,其中该透光导电层具有对应该等微发光二极 管像素的共同电极;

设置一色层于该透光导电层上,其中该色层系为RGB色层。

- 2.如权利要求1所述的制造方法,其特征在于,该N型半导体层包括一N型掺杂层及一N型缓冲层,该N型掺杂层位于该N型缓冲层与该发光层之间。

- 3.如权利要求1所述的制造方法,其特征在于,该P型半导体层还包括一P型掺杂层及一P型缓冲层,该P型掺杂层位于该P型缓冲层与该发光层之间。

- 4. 如权利要求1所述的制造方法,其特征在于,另包括一步骤:将该驱动芯片区块另与一电路板电性连接,其中该驱动芯片区块系为从该驱动晶圆上切割分离的驱动芯片。

- 5. 如权利要求4所述的制造方法,其特征在于,该透光导电层藉由一导电胶另与该电路 板电性连接。

- 6.如权利要求1所述的制造方法,其特征在于,该透光导电层藉由一导电胶电性连接该驱动芯片区块。

- 7.如权利要求1所述的制造方法,其特征在于,该透光导电层包括一披覆有一IT0导电膜的玻璃层,该IT0导电膜与各该微发光二极管像素电性连接。

- 8. 如权利要求1所述的制造方法,其特征在于,该色层系为滤光片。

- 9. 如权利要求1所述的制造方法,其特征在于,该色层系以喷涂量子点方式形成。

- 10.如权利要求1所述的制造方法,其特征在于,于接合该发光二极管区块与该驱动芯片区块的步骤之前、于制备该发光二极管晶圆的步骤之后,另包括一步骤:将该发光二极管区块从该发光二极管晶圆切割分离;其中接合该发光二极管区块与该驱动芯片区块的步骤,系该发光二极管区块与具有该驱动芯片区块的该驱动电路晶圆接合。

- 11.如权利要求1所述的制造方法,其特征在于,于接合该发光二极管区块与该驱动芯片区块的步骤之前、于制备该发光二极管晶圆及该驱动电路晶圆的步骤之后,另包括一步骤:将该发光二极管区块及该驱动芯片区块分别从该发光二极管晶圆及该驱动电路晶圆切割分离。

- 12.如权利要求1所述的制造方法,其特征在于,接合该发光二极管区块及该驱动芯片区块的步骤,系将该具有该发光二极管区块的发光二极管晶圆与该具有该驱动芯片区块的驱动电路晶圆相接合。

- 13.如权利要求1所述的制造方法,其特征在于,另包括一步骤,将非导电胶注入该等沟槽。

- 14.一种微发光二极管显示模块,包括:

- 一驱动芯片区块,具有多个像素电极;

- 一发光二极管区块,设于该驱动芯片区块,且具有二半导体层、及多个沟槽,该发光层位于该第一及该第二半导体层之间,该二半导体层其中一者电性连接该等像素电极、另一者连接一透光导电层,该发光二极管区块介于该透光导电层与该驱动芯片区块之间,该等沟槽界定出多个呈矩阵排列的微发光二极管像素,各该沟槽至少穿透该发光层、及连接该等像素电极的半导体层,各该微发光二极管像素对应一该像素电极,该二半导体层其中一者系为N型半导体层、另一者系为P型半导体层;

- 一电路板,电性连接该驱动芯片区块,且该驱动电路芯片区块介于该发光二极管区块与该电路板之间;

- 一色层,设于该透光导电层,该透光导电层位于该色层与该发光二极管区块之间,该色层系为RGB色层。

- 15. 如权利要求14所述的微发光二极管显示模块,其特征在于,该N型半导体层包括一N型掺杂层及一N型缓冲层,该N型掺杂层位于该N型缓冲层与该发光层之间。

- 16.如权利要求14所述的微发光二极管显示模块,其特征在于,该P型半导体层还包括一P型掺杂层及一P型缓冲层,该P型掺杂层位于该P型缓冲层与该发光层之间。

- 17. 如权利要求14所述的微发光二极管显示模块,其特征在于,该透光导电层与该电路板之间设有一导电胶,该导电胶分别电性连接该透光导电层及该电路板。

- 18. 如权利要求14所述的微发光二极管显示模块,其特征在于,该透光导电层与该驱动芯片区块之间设有一导电胶,该导电胶分别电性连接该透光导电层及该驱动芯片区块。

- 19. 如权利要求14所述的微发光二极管显示模块,其特征在于,该透光导电层包括一披覆有一IT0导电膜的玻璃层,该IT0导电膜与各该微发光二极管像素电性连接。

- 20.如权利要求14所述的微发光二极管显示模块,其特征在于,该透光导电层系为IT0 导电层。

- 21. 如权利要求14所述的微发光二极管显示模块,其特征在于,该色层系为滤光片。

- 22.如权利要求14所述的微发光二极管显示模块,其特征在于,该色层系以喷涂量子点方式形成。

- 23. 如权利要求14所述的微发光二极管显示模块,其特征在于,各该沟槽内填充有非导电胶。

- 24. 如权利要求14所述的微发光二极管显示模块,其特征在于,各该沟槽未穿透该连接 该透光导电层的半导体层。

- 25.如权利要求14所述的微发光二极管显示模块,其特征在于,各该沟槽穿透连接该透光导电层的半导体层。

# 微发光二极管显示模块及其制造方法

#### 技术领域

[0001] 本发明系关于一种发光二极管,特别系一种微发光二极管显示模块及其制造方法

#### 背景技术

[0002] 传统发光二极管 (Light Emitting Diode, LED) 多用于LCD (Liquid Crystal Device) 的背光源或是直接做为发光像素点使用,然而后者由于分辨率不足的因素,多用于大型的广告灯板,较少应用于消费性电子产品。

[0003] 近年来开始发展一种新的显示技术-微发光二极管(Micro LED),主要是将LED进行微小化、薄膜化、以及阵列化,其尺寸大小为微米级。Micro LED除了具有以往无机LED的特点-高色彩饱和度、高效率、高亮度、反应迅速等,并且应用于显示设备时,仅需透过自发光而无需背光源即可达到显示的目的,更具节能、机构简易、轻薄等优势,最重要的是,微发光二极管还具有超高分辨率的特性。

[0004] 除此之外,微发光二极管相较于有机发光二极管,其色彩更容易准确的调整,且具有更长的发光寿命、更高的亮度、较少的影像残留以及具有较佳的材料稳定性等优点。

[0005] 一般利用如台湾专利TW 201640697A或论文「Zhao Jun Liu et al., Monolithic LED Microdisplay on Active Matrix Substrate Using Flip-Chip Technology, IEEE Journal Of Selected Topics In Quantum Electronics, pp.1-5 (2009) 」所述的微发光二极管来制造显示模块时,通常需要分批制造不同颜色的微发光二极管,再将其分批大量转贴到控制电路板上,再利用物理沉积制程来设置保护层以及电极,之后再进行封装以完成一个微发光二极管显示模块。

[0006] 然而,分批转贴不同颜色的微发光二极管的过程中,因为每个微发光二极管的体积十分细小,并不易转移(拾取与放置)以及接线连接(Wire Bonding),进而产生良率不佳、制造缓慢以及成本耗费等问题。

## 发明内容

[0007] 本发明可以将多个微发光二极管以阵列的方式生成并设置于驱动芯片区块上,使驱动芯片上的像素电极个别驱动每个微发光二极管像素,并且使用透光导电层或微发光二极管内部的结构(例如半导体层)来作为多个像素的共同电极,如此一来,每一个微发光二极管即可经由驱动芯片寻址控制而单独驱动点亮。

[0008] 另外,为了使微发光二极管显示模块可以全色显示,可另外设置RGB(Red, Green, Blue)色层,例如设置RGB滤光片或喷涂量子点。透过此种结构即可制作高分辨率的微发光二极管显示模块;并且可降低转移过程中产生良率不佳等问题。

[0009] 为了达成上述目的,本发明提供一种微发光二极管显示模块的制造方法,包括以下步骤:制备一发光二极管晶圆及一驱动电路晶圆,其中该发光二极管晶圆的部分区域界定为一发光二极管区块,该驱动电路晶圆的一芯片大小的区域界定为一驱动芯片区块,其中该发光二极管区块具有一第一半导体层、一发光层、及一第二半导体层,该发光层设于该

第一半导体层及该第二半导体层之间,该第一半导体层连接一基材,该第一及该第二半导体层其中一者系为N型半导体层、另一者系为P型半导体层;接合该发光二极管区块与该驱动芯片区块,其中该第二半导体层与该驱动芯片区块的多个像素电极电性连接;去除该基材;蚀刻该发光二极管区块,而形成交错排列的多个沟槽,其中该等沟槽界定出呈矩阵排列的多个微发光二极管像素,各该微发光二极管像素对应一该像素电极;设置一透光导电层于该第一半导体层上,其中该透光导电层具有对应该等微发光二极管像素的共同电极;设置一色层于该透光导电层上,其中该色层系为RGB色层。

[0010] 为了达成上述目的,本发明提供一种微发光二极管显示模块,包括:一驱动芯片区块,具有多个像素电极;一发光二极管区块,设于该驱动芯片区块,且具有二半导体层、及多个沟槽,该发光层位于该第一及该第二半导体层之间,该二半导体层其中一者电性连接该等像素电极、另一者连接一透光导电层,该发光二极管区块介于该透光导电层与该驱动芯片区块之间,该等沟槽界定出多个呈矩阵排列的微发光二极管像素,各该沟槽至少穿透该发光层、及连接该等像素电极的半导体层,各该微发光二极管像素对应一该像素电极,该二半导体层其中一者系为N型半导体层、另一者系为P型半导体层;一电路板,电性连接该驱动芯片区块,且该驱动电路芯片区块介于该发光二极管区块与该电路板之间;一色层,设于该透光导电层,该透光导电层位于该色层与该发光二极管区块之间,该色层系为RGB色层。

## 附图说明

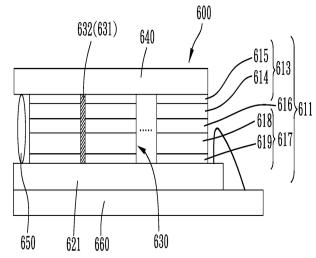

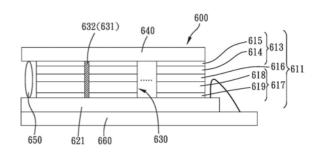

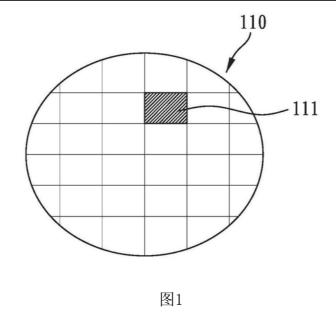

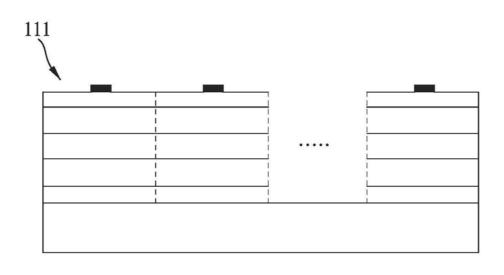

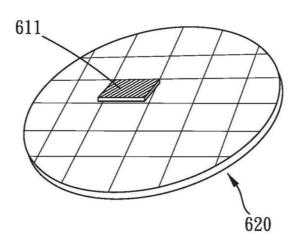

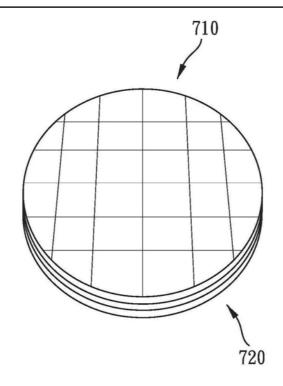

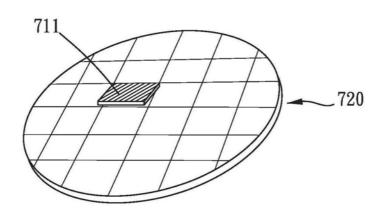

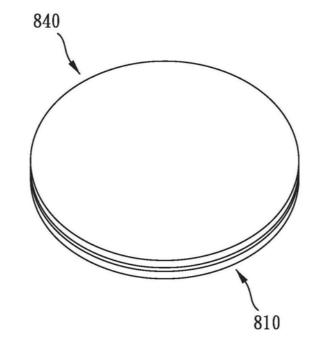

[0011] 图1系为本发明的发光二极管晶圆的示意图。

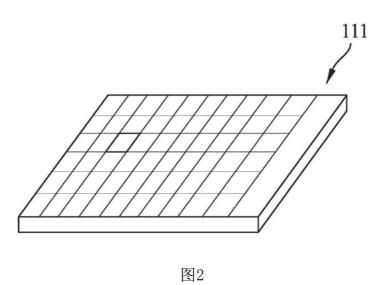

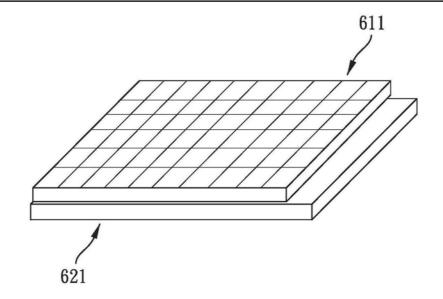

[0012] 图2系为本发明的发光二极管区块的示意图。

[0013] 图3系为本发明的发光二极管区块的剖面示意图。

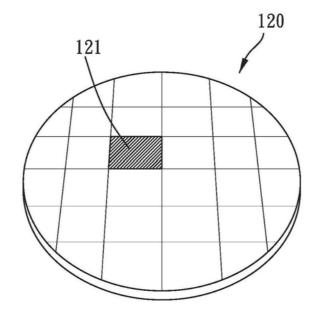

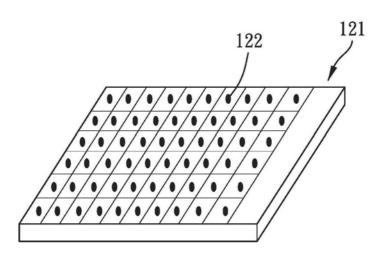

[0014] 图4系为本发明的驱动电路晶圆的示意图。

[0015] 图5系为本发明的驱动芯片区块的示意图。

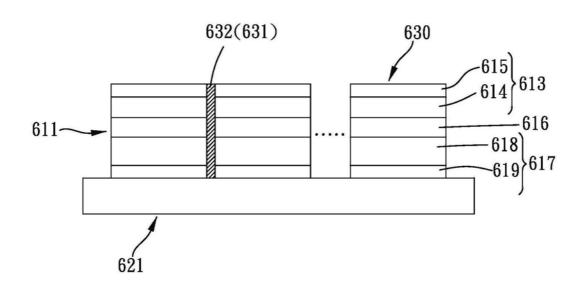

[0016] 图6A至图6I系为第一实施例及其它替代实施例的示意图。

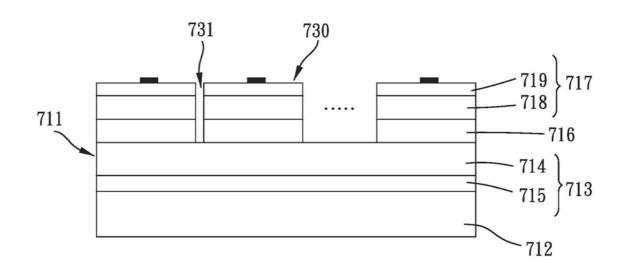

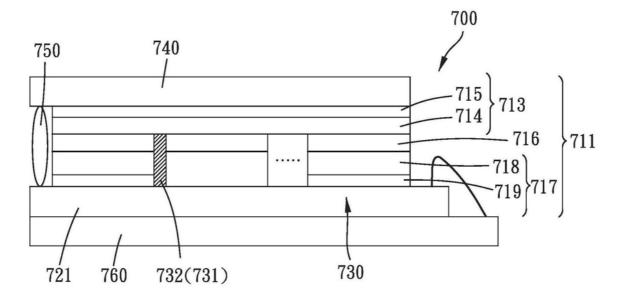

[0017] 图7A至图7L系为第二实施例及其它替代实施例的示意图。

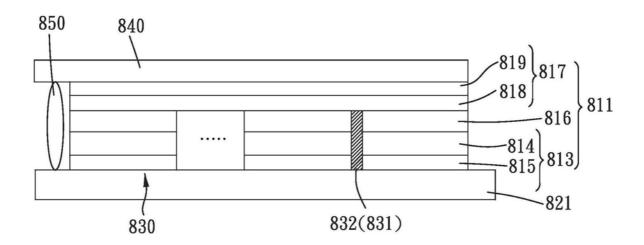

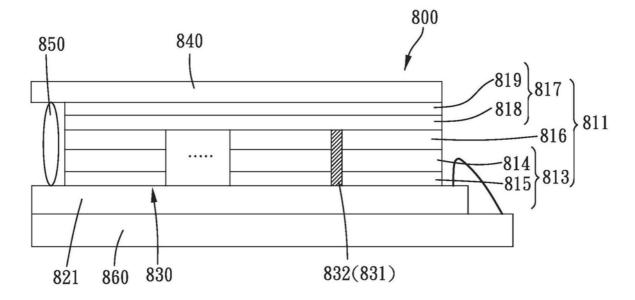

[0018] 图8A至图8G系为第三实施例及其它替代实施例的示意图。

[0019] 图9A至图9H系为第四实施例及其它替代实施例的示意图。

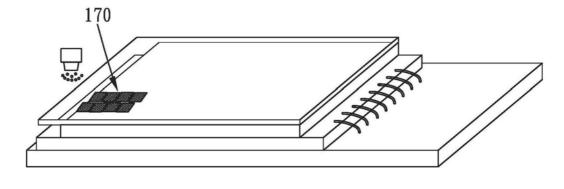

[0020] 图10至11为本发明的设置色层步骤的示意图。

[0021] 图10A为本发明的色层的局部放大图。

[0022] 符号说明

[0023] 110:发光二极管晶圆 800:微发光二极管显示模块

[0024] 111:发光二极管区块 810:发光二极管晶圆

[0025] 120:驱动电路晶圆 811:发光二极管区块

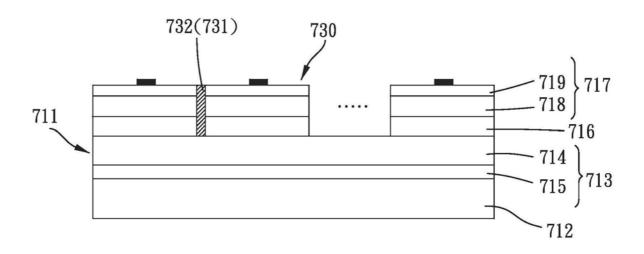

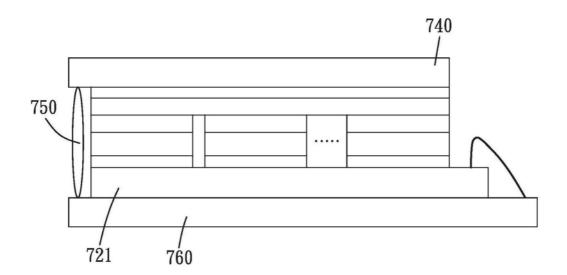

[0026] 121:驱动芯片区块 812:基材

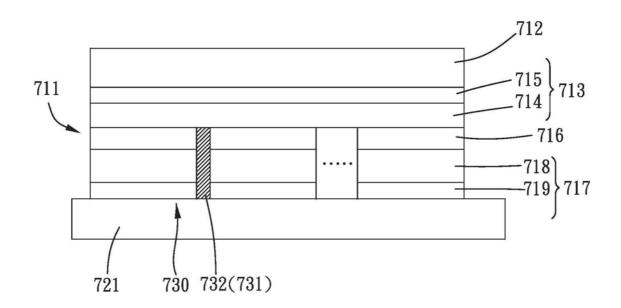

[0027] 122: 像素电极 813:N型半导体层

[0028] 600: 微发光二极管显示模块 814: N型掺杂层

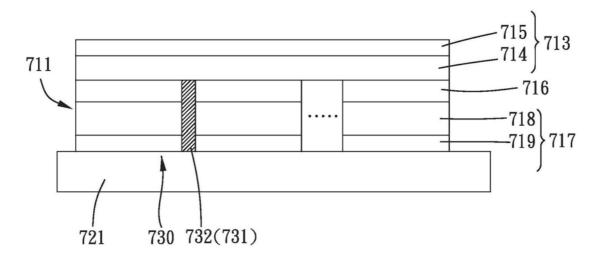

[0029] 610:发光二极管晶圆 815:N型缓冲层

[0030] 611:发光二极管区块 816:发光层

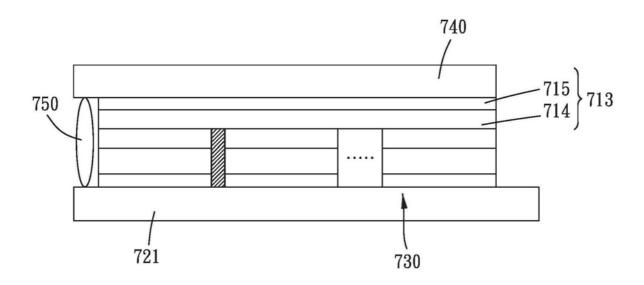

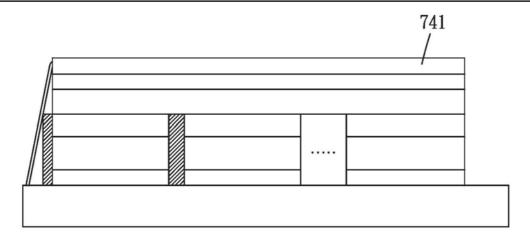

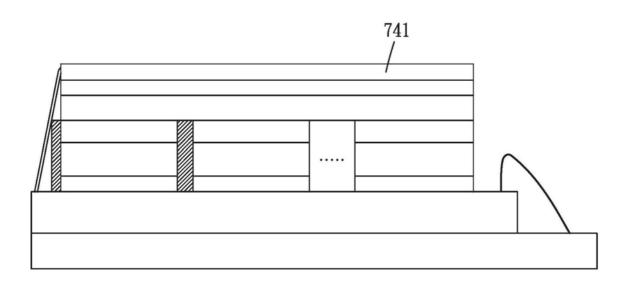

[0031] 612:基材 817:P型半导体层

| [0032] | 613:N型半导体层     | 818:P型掺杂层      |

|--------|----------------|----------------|

| [0033] | 614:N型掺杂层      | 819:P型缓冲层      |

| [0034] | 615:N型缓冲层      | 821:驱动芯片区块     |

| [0035] | 616:发光层        | 830:微发光二极管像素   |

| [0036] | 617:P型半导体层     | 831:沟槽         |

| [0037] | 618:P型掺杂层      | 832:非导电胶       |

| [8800] | 619:P型缓冲层      | 840:透光导电层      |

| [0039] | 620:驱动电路晶圆     | 850:导电胶        |

| [0040] | 621:驱动芯片区块     | 860:电路板        |

| [0041] | 630:微发光二极管像素   | 900:微发光二极管显示模块 |

| [0042] | 631:沟槽         | 910:发光二极管晶圆    |

| [0043] | 632:非导电胶       | 911:发光二极管区块    |

| [0044] | 640:透光导电层      | 912:蓝宝石基材      |

| [0045] | 650:导电胶        | 913:N型半导体层     |

| [0046] | 660:电路板        | 914:N型掺杂层      |

| [0047] | 700:微发光二极管显示模块 | 915:N型缓冲层      |

| [0048] | 710:发光二极管晶圆    | 916:发光层        |

| [0049] | 711:发光二极管区块    | 917:P型半导体层     |

| [0050] | 712:基材         | 918:P型掺杂层      |

| [0051] | 713:N型半导体层     | 919:P型缓冲层      |

| [0052] | 714:N型掺杂层      | 920:驱动电路晶圆     |

| [0053] | 715:N型缓冲层      | 921:驱动芯片区块     |

| [0054] | 716:发光层        | 930:微发光二极管像素   |

| [0055] | 717:P型半导体层     | 931:沟槽         |

| [0056] | 718:P型掺杂层      | 932:非导电胶       |

| [0057] | 719:P型缓冲层      | 950:导电胶        |

| [0058] | 720:驱动电路晶圆     | 960:电路板        |

| [0059] | 721:驱动芯片区块     | 970:凸出部        |

| [0060] | 730:微发光二极管像素   | 170:色层         |

| [0061] | 731:沟槽         | 171:像素区域       |

| [0062] | 732:非导电胶       | 172:像素区域       |

| [0063] | 740:透光导电层      | 173:像素区域       |

| [0064] | 741:透光导电层      | 180:色层         |

| [0065] | 750:导电胶        |                |

## 具体实施方式

760:电路板

[0066]

[0067] 以下仅以实施例说明本发明可能的实施态样,然并非用以限制本发明所欲保护的范畴,合先叙明。

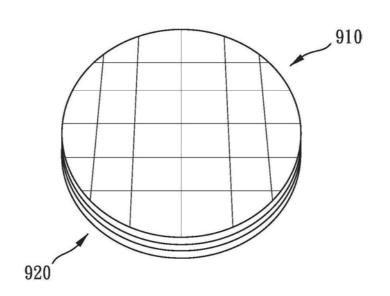

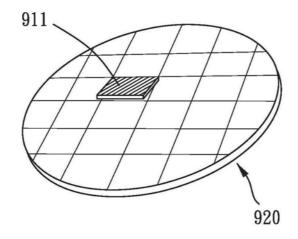

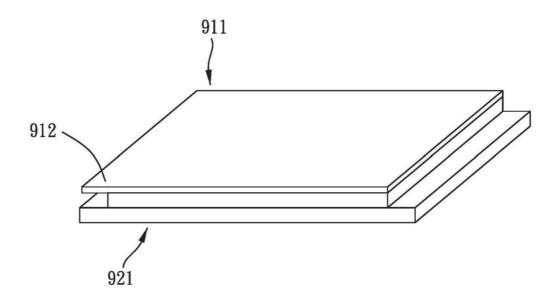

[0068] 请参阅图1至5,其显示本发明制造的初所需制备的发光二极管晶圆110、发光二极管区块111、驱动电路晶圆120、以及驱动芯片区块121。为便于描述各种实施例,在说明书未明确说明前,发光二极管区块111可以系代表发光二极管晶圆110的部分区域(还与该发光二极管晶圆110的其它部分一体相连)、亦可以是已从该发光二极管晶圆110切割分离的区块;该驱动芯片区块121可以系代表该驱动电路晶圆120的部分区域(还与该驱动电路晶圆120的其它部分一体相连)、或是已从该驱动电路晶圆120切割分离而成的驱动芯片。各该驱动芯片区块121上具有多个像素电极122,各该像素电极122可独立驱动一微发光二极管像素。

[0069] 也就是说,将该发光二极管区块111从该发光二极管晶圆110切割分离或/及该驱动芯片区块121从该驱动电路晶圆120切割分离的时间点,可以在制备该发光二极管晶圆及该驱动电路晶圆的步骤与将该驱动芯片区块与一电路板电性连接的步骤之间的任何时候皆可。

[0070] 于本发明中,在制作该发光二极管晶圆110及该驱动电路晶圆120时,亦可留有部分空白区域(例如部分区域不设置半导体层、发光层、像素电极),供之后设置电极连接垫或多道切割程序之用。

[0071] 此外,于各图中的部分线条,仅系用以表示后续制程如蚀刻或切割的假想线,实际上可以不具有该些线条。

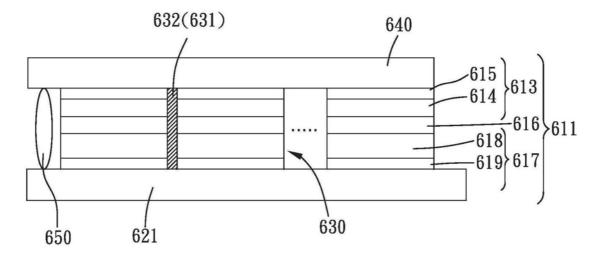

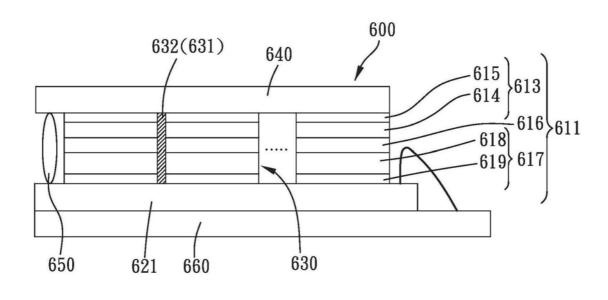

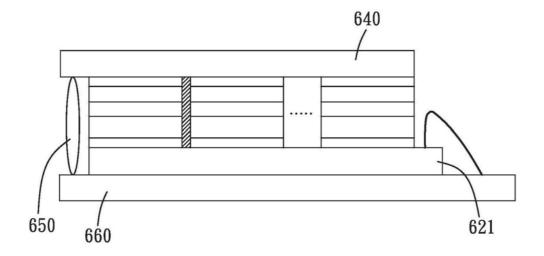

[0072] 请参阅图6C、6D、6E、6F、6G、6H,其显示本发明的第一实施例,本实施例的微发光二极管显示模块600的制造方法包括以下步骤。

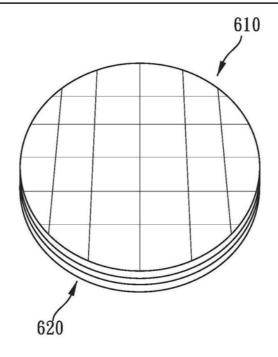

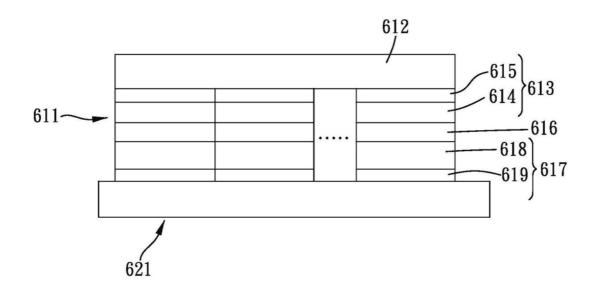

[0073] 一开始,制备一发光二极管晶圆610及一驱动电路晶圆620。该发光二极管晶圆610的部分区域界定为一发光二极管区块611,该驱动电路晶圆620的一芯片大小的区域界定为一驱动芯片区块621,其中该发光二极管区块611具有一第一半导体层、一发光层616、及一第二半导体层,该发光层616设于该第一半导体层及该第二半导体层之间,该第一半导体层连接一基材612。更明确的说,该第一及该第二半导体层其中一者系为N型半导体层、另一者系为P型半导体层,于本实施例,该第一半导体层系为N型半导体层613,该第二半导体层系为P型半导体层617。其中,该N型半导体层613包括一N型掺杂层614及一N型缓冲层615,该N型掺杂层614位于该N型缓冲层615与该发光层616之间。该P型半导体层617还包括一P型掺杂层618及一P型缓冲层619,该P型掺杂层618位于该P型缓冲层619与该发光层616之间,于某些实施例,亦可不具有N型或P型缓冲层。更进一步说,该驱动芯片区块621具有多个可独立驱动的像素电极以及集成电路。该N型掺杂层614系为富含电子的负极半导体层,该P型掺杂层618系为富含电洞的正极半导体层。而该N型及该P型缓冲层615、619则是该N型掺杂层极614及该P型掺杂层618与外界材料相连接的过渡层。

[0074] 接着,请参阅图6C、6D,将该发光二极管区块611与该驱动芯片区块621接合,该P型半导体层617与该驱动芯片区块621的多个像素电极电性连接。较佳地,为避免影响材料性质,该发光二极管区块611与该驱动芯片区块621系以低于摄氏200度的低温混合连接技术进行接合,使该发光二极管区块611与该驱动芯片区块621的像素电极黏合,可理解的是,亦可另设有电极连接垫,以便于黏合或导电。要说明的是,于本实施例,该发光二极管区块611及该驱动芯片区块621系为已分别从该发光二极管晶圆及该驱动电路晶圆切割分离的区块,之后才进行此接合步骤。此外,于另一实施例,如图6A,亦可将整个发光二极管晶圆610

与驱动电路晶圆620接合;抑或是,如图6B,先从该发光二极管晶圆切割分离出该发光二极管区块611,再将该发光二极管区块611接合至该驱动电路晶圆620。

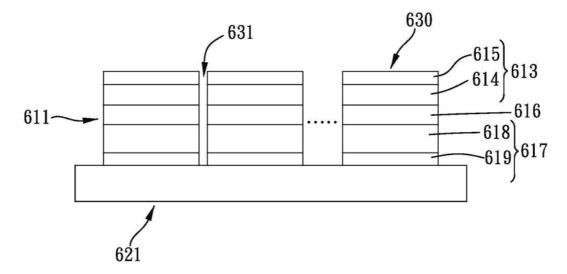

[0075] 接着请参阅图6E,将基材612去除,并且蚀刻该发光二极管区块611,而形成交错排列的多个沟槽631,该等沟槽631界定出呈矩阵排列的多个微发光二极管像素630(微发光二极管阵列),各该微发光二极管像素630对应一该像素电极,如此一来,即可透过各该像素电极单独供电给相对应的微发光二极管像素630。要说明的是,各该微发光二极管像素630的尺寸通常系为微米级的。

[0076] 接着,请参阅图6F,将非导电胶632注入该等沟槽631,以增加该等微发光二极管像素630之间的结构强度。于其它实施例中,亦可不进行此步骤。

[0077] 接下来,请参阅图6G,设置一透光导电层640于该N型半导体层613上。更明确地说,该透光导电层640包括一披覆有一IT0导电膜的玻璃层,该IT0导电膜与各该微发光二极管像素630电性连接,该IT0导电膜即为对应该等微发光二极管像素630的共同电极。并且,该透光导电层640藉由一导电胶650(抑或是其它导体)电性连接该驱动芯片区块621。透过该IT0导电膜与该等像素电极之间的电位差,即可控制各该微发光二极管像素630发亮。

[0078] 接着,请参阅图6H,将该驱动芯片区块621与一电路板660(印刷电路板或软性电路板)电性连接,进一步说,该驱动芯片区块621系设置于该电路板660上,并透过打线接合(Wire Bonding)的方式使该驱动芯片区块621与该电路板660电性连接。要说明的是,进行此步骤时,该驱动芯片区块621与该发光二极管区块611皆系已从该驱动电路晶圆及该发光二极管晶圆上切割分离的区块(即为独立的发光二极管像素阵列以及驱动芯片)。于另一实施例中,例如图6I,该导电胶650亦可不连接该驱动芯片区块621,而系连接该透光导电层640与该电路板660。于某些实施例中,亦可不设有导电胶,而将该IT0导电膜电性连接其它外部电源,只要该IT0导电膜与该像素电极之间具有电位差即可,即可使各微发光二极管像素发亮。

[0079] 经过上述步骤,即制造出如图6H所示的微发光二极管显示模块600。该微发光二极管显示模块包括该驱动芯片区块621、该发光二极管区块611、该透光导电层640、及该电路板660。该驱动芯片区块621具有该多个像素电极。该发光二极管区块611设于该驱动芯片区块621上。该发光二极管区块611具有该第一半导体层、该发光层616、该第二半导体层、及该多个沟槽631。该发光层616位于该第一及该第二半导体层之间,该第二半导体层电性连接该等像素电极,该等沟槽631界定出该多个呈矩阵排列的微发光二极管像素630,各该沟槽631穿透该第一半导体层、该第二半导体层及该发光层616。各该微发光二极管像素630对应一该像素电极,该第一及该第二半导体层其中一者系为N型半导体层613、另一者系为P型半导体层617。各该沟槽631内填充有非导电胶632。

[0080] 该透光导电层640设于该发光二极管区块611且连接该第一半导体层,该发光二极管区块611介于该透光导电层640与该驱动芯片区块621之间。该电路板660电性连接该驱动芯片区块621,且该驱动芯片区块621介于该发光二极管区块611与该电路板660之间。该透光导电层640与该驱动芯片区块621之间设有一导电胶650,该导电胶650分别电性连接该透光导电层640及该驱动芯片区块621。该透光导电层640包括一披覆有一IT0导电膜的玻璃层,该IT0导电膜与各该微发光二极管像素630电性连接。于另一实施例,如图6I,亦可于该透光导电层640与该驱动芯片区块621之间设有该导电胶650,该导电胶650分别电性连接该

透光导电层640及该驱动芯片区块621。

[0081] 请参阅图7A、7B、7E、7F、7G、7H、7I,其显示本发明的第二实施例,本实施例的微发光二极管显示模块700的制造方法包括以下步骤。

[0082] 一开始,制备一发光二极管晶圆710及一驱动电路晶圆720。该发光二极管晶圆710的部分区域界定为一发光二极管区块711,该驱动电路晶圆720的一芯片大小的区域界定为一驱动芯片区块721,其中该发光二极管区块711具有一第一半导体层、一发光层716、及一第二半导体层,该发光层716设于该第一半导体层及该第二半导体层之间,该第一半导体层连接一基材712,该第一及该第二半导体层其中一者系为N型半导体层、另一者系为P型半导体层。更明确地说,该第一半导体层系为N型半导体层713,该第二半导体层系为P型半导体层717。其中,该N型半导体层713包括一N型掺杂层714及一N型缓冲层715,该N型掺杂层714位于该N型缓冲层715与该发光层716之间。该P型半导体层717还包括一P型掺杂层718及一P型缓冲层719,该P型掺杂层718位于该P型缓冲层719与该发光层716之间,于某些实施例,亦可不具有N型或P型缓冲层。

[0083] 请参阅图7A,蚀刻该发光二极管区块711,而形成交错排列的多个沟槽731,该等沟槽731界定出呈矩阵排列的多个微发光二极管像素730(如同微发光二极管阵列),各该沟槽731至少穿透该P型半导体层717及该发光层716。进一步说,各该沟槽731未穿透该N型半导体层713,该N型半导体层713系为对应该等微发光二极管像素730的共同电极。于其它实施例,亦可以使各沟槽穿透N型半导体层或仅穿透N型掺杂层,只要让透光导电层具有共同电极即可。可理解的是,于进行蚀刻该发光二极管区块的步骤时,可以系蚀刻整个发光二极管晶圆、抑或是仅蚀刻经过切割分离的发光二极管区块711。

[0084] 接着,请参阅图7B,将非导电胶732注入该等沟槽731,以增加该等微发光二极管像素730之间的结构强度。于某些实施例中,亦可不进行此步骤。

[0085] 接着,请参阅图7E、7F,接合该发光二极管区块711及该驱动芯片区块721,其中该P型半导体层717电性连接该驱动芯片区块721的多个像素电极。较佳地,为避免影响材料性质,该发光二极管区块711与该驱动芯片区块721系以低于摄氏200度的低温混合连接技术进行接合。且各该微发光二极管像素730对应一该像素电极。如此一来,即可透过各该像素电极单独驱动相对应的微发光二极管像素730。要说明的是,各该微发光二极管像素730的尺寸通常系为微米级的。于本实施例,该发光二极管区块711及该驱动芯片区块721系为分别从该发光二极管晶圆710及该驱动电路晶圆720切割分离的区块,之后才进行此接合步骤。可理解的是,于另一实施例,如图7C,亦可将整个发光二极管晶圆710与驱动电路晶圆720接合,于后续步骤再进行切割分离;抑或是,如图7D,先从该发光二极管晶圆710切割分离出该发光二极管区块711,再将该发光二极管区块711接合至该驱动电路晶圆720中相对应的位置上,之后再进行切割。

[0086] 接着,请参阅图7G,将基材去除。

[0087] 接下来,请参阅图7H,设置一透光导电层740于该N型半导体层713上,其中该透光导电层740具有对应该等微发光二极管像素730的共同电极,进一步说,该透光导电层740包括一披覆有一IT0导电膜的玻璃层,该IT0导电膜与各该微发光二极管像素730电性连接,该IT0导电膜即为对应该等微发光二极管像素730的共同电极。此外,该透光导电层740藉由一导电胶750电性连接该驱动芯片区块721,透过该IT0导电膜与该等像素电极之间的电位差,

即可控制各该微发光二极管像素730发亮。于另一实施例,如图7K及图7L,透光导电层741亦可以是以物理溅镀方式(Physical Sputtering)而形成的ITO导电层,而不具有玻璃层。

[0088] 接下来,请参阅图7I,将该驱动芯片区块721另与一电路板760电性连接,要说明的是,进行此步骤时,该驱动芯片区块721与该发光二极管区块711皆系已从该驱动电路晶圆720及该发光二极管晶圆710上切割分离的区块(即为独立的发光二极管像素阵列以及驱动芯片)。于另一实施例中,例如图7J,导电胶750亦可不连接该驱动芯片区块721,而系连接该透光导电层740与该电路板760。于其它实施例中,亦可不设有导电胶,而将该IT0导电膜以其它导体电性连接其它外部电源,只要IT0导电膜与像素电极之间具有电位差,即可驱动各微发光二极管像素发亮。

[0089] 本实施例经过上述步骤,即制造出如图7I所示的微发光二极管显示模块700。该微发光二极管显示模块700包括该驱动芯片区块721、该发光二极管区块711、该透光导电层740、及该电路板760。该驱动芯片区块721具有该多个像素电极。该发光二极管区块711设于该驱动芯片区块721上。该发光二极管区块711具有该第一半导体层、该发光层716、该第二半导体层、及该多个沟槽731。该发光层716位于该第一及该第二半导体层之间,该第二半导体层电性连接该等像素电极,该等沟槽731界定出该多个呈矩阵排列的微发光二极管像素730,各该沟槽731穿透该第二半导体层及该发光层716。各该微发光二极管像素730对应一该像素电极,该第一及该第二半导体层其中一者系为N型半导体层713、另一者系为P型半导体层717。各该沟槽731内填充有非导电胶732。

[0090] 该透光导电层740设于该发光二极管区块711上且连接该第一半导体层,该发光二极管区块711介于该透光导电层740与该驱动芯片区块721之间。该电路板760电性连接该驱动芯片区块721,且该驱动芯片区块721介于该发光二极管区块711与该电路板760之间。该透光导电层740与该驱动芯片区块721之间设有一导电胶750,该导电胶750分别电性连接该透光导电层740及该驱动芯片区块721。该透光导电层740包括一披覆有一IT0导电膜的玻璃层,该IT0导电膜与各该微发光二极管像素730电性连接(当然亦可如图7L仅具有IT0导电层而不具有玻璃层)。于另一实施例,如图7J,亦可将该导电胶750设于该透光导电层740与该驱动芯片区块721之间,该导电胶750分别电性连接该透光导电层740及该驱动芯片区块721。

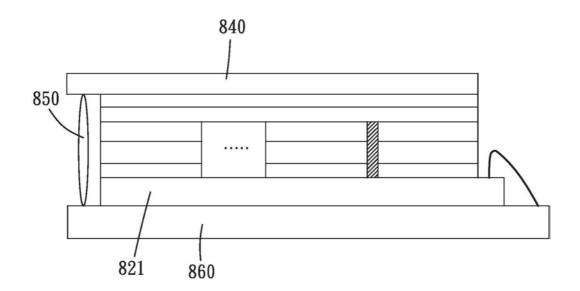

[0091] 请参阅图8A、8B、8C、8D、8E、8F,其显示本发明的第三实施例,本实施例的微发光二极管显示模块800的制造方法包括以下步骤。

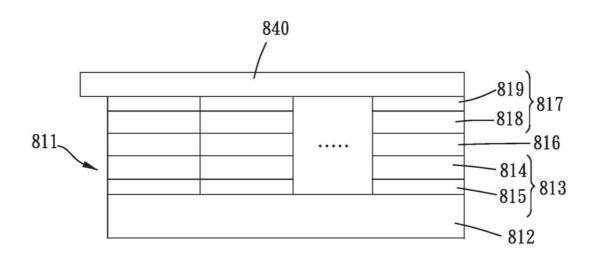

[0092] 一开始,制备一发光二极管晶圆810及一驱动电路晶圆。该发光二极管晶圆810的部分区域界定为一发光二极管区块811,该驱动电路晶圆820的一芯片大小的区域界定为一驱动芯片区块821,其中该发光二极管区块811具有一第一半导体层、一发光层816、及一第二半导体层,该发光层816设于该第一半导体层及该第二半导体层之间,该第一半导体层连接一基材812,该第一及该第二半导体层其中一者系为N型半导体层、另一者系为P型半导体层。更明确地说,该第一半导体层系为N型半导体层813,该第二半导体层系为P型半导体层817。其中,该N型半导体层813包括一N型掺杂层814及一N型缓冲层815,该N型掺杂层814位于该N型缓冲层815与该发光层816之间。该P型半导体层817还包括一P型掺杂层818及一P型缓冲层819,该P型掺杂层818位于该P型缓冲层819与该发光层816之间,于某些实施例,亦可不具有N型或P型缓冲层。

[0093] 将该发光二极管区块811的P型半导体层817与一透光导电层840接合。进一步说,该透光导电层840包括一披覆有一IT0导电膜的玻璃层,该IT0导电膜与该P型半导体层817电性连接。于本实施例,如图8A所示,本步骤实际上系将该发光二极管晶圆810与该透光导电层840接合,且该透光导电层840系为IT0玻璃晶圆。此步骤结束之后,再将该发光二极管区块811从该发光二极管晶圆810切割分离,如图8B所示。于其它实施例,亦可于后续步骤再将发光二极管区块811从该发光二极管晶圆810切割分离

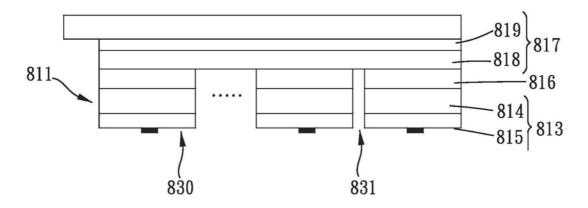

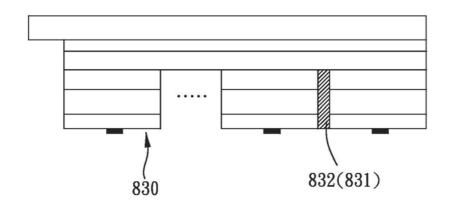

[0094] 接着,如图8C所述,去除该基材812;且蚀刻该发光二极管区块811。该发光二极管区块811形成交错排列的多个沟槽831,该等沟槽831界定出呈矩阵排列的多个微发光二极管像素830,各该沟槽831至少穿透该N型半导体层813及该发光层816。于本实施例,各该沟槽831未穿透该P型半导体层813,该IT0导电膜及该P型半导体层813系为对应该等微发光二极管像素830的共同电极。于其它实施例,亦可以使各沟槽穿透N型半导体层或仅穿透N型掺杂层。可理解的是,于进行蚀刻该发光二极管区块的步骤时,亦可以蚀刻整个发光二极管晶圆。

[0095] 接着,请参阅图8D,将非导电胶832注入该等沟槽831,以增加该等微发光二极管像素830之间的结构强度。于某些实施例中,亦可不进行此步骤。

[0096] 接着,请参阅图8E,接合该发光二极管区块811及该驱动芯片区块821,其中该N型半导体层813电性连接该驱动芯片区块821的多个像素电极,较佳地,为避免影响材料性质,该发光二极管区块811与该驱动芯片区块821系以低于摄氏200度的低温混合连接技术进行接合。各该微发光二极管像素830对应一该像素电极,如此一来,即可透过各该像素电极单独供电给相对应的微发光二极管像素830。要说明的是,各该微发光二极管像素830的尺寸通常系为微米级的。于本实施例,该发光二极管区块811及该驱动芯片区块821系为已分别从该发光二极管晶圆及该驱动电路晶圆切割分离的区块,之后才进行此接合步骤。可理解的是,于其它实施例,亦可将整个发光二极管晶圆与驱动电路晶圆接合;抑或是,先从该发光二极管晶圆切割分离出该发光二极管区块,再将该发光二极管区块接合至该驱动电路晶圆中像对应的位置上,于后需步骤再切割该驱动电路晶圆。

[0097] 接下来请参阅图8F,将该驱动芯片区块821另与一电路板860电性连接,要说明的是,进行此步骤时,该驱动芯片区块821与该发光二极管区块811皆系已从该驱动电路晶圆及该发光二极管晶圆上切割分离的区块(即为独立的发光二极管像素阵列以及驱动芯片)。于本实施例,将该透光导电层840藉由一导电胶850电性连接该驱动芯片区块821,如此一来,透过该IT0导电膜与该等像素电极之间的电位差,即可控制各该微发光二极管像素830发亮。于其它实施例,如图8G,亦可将导电胶850电性连接该透光导电层840及该电路板860,而不连接驱动芯片区块821。于某些实施例中,亦可不设有导电胶,而将该IT0导电膜以其它导体电性连接至其它外部电源,只要IT0导电膜与像素电极之间具有电位差即可,即可使各微发光二极管像素发亮。

[0098] 本实施例经过上述步骤,即可制造出如图8F所示的微发光二极管显示模块800。该微发光二极管显示模块包括该驱动芯片区块821、该发光二极管区块811、该透光导电层840、及该电路板860。该驱动芯片区块821具有该多个像素电极。该发光二极管区块811设于该驱动芯片区块821上。该发光二极管区块811具有该第一半导体层、该发光层816、该第二半导体层、及该多个沟槽831。该发光层816位于该第一及该第二半导体层之间,该第二半导

体层电性连接该等像素电极,该等沟槽831界定出该多个呈矩阵排列的微发光二极管像素830,各该沟槽831穿透该第二半导体层及该发光层816。各该微发光二极管像素830对应一该像素电极,该第一及该第二半导体层其中一者系为N型半导体层813、另一者系为P型半导体层817。各该沟槽831内填充有非导电胶832。

[0099] 该透光导电层840设于该发光二极管区块811且连接该第一半导体层,该发光二极管区块811介于该透光导电层840与该驱动芯片区块821之间。该电路板860电性连接该驱动芯片区块821,且该驱动电路芯片区块介于该发光二极管区块811与该电路板860之间。该透光导电层840与该驱动芯片区块821之间设有一导电胶850,该导电胶850分别电性连接该透光导电层840及该驱动芯片区块821。该透光导电层840包括一披覆有一IT0导电膜的玻璃层,该IT0导电膜与各该微发光二极管像素830电性连接。于另一实施例,如图8G,亦可将该导电胶850设于该透光导电层840与该驱动芯片区块821之间,该导电胶850分别电性连接该透光导电层840及该驱动芯片区块821。

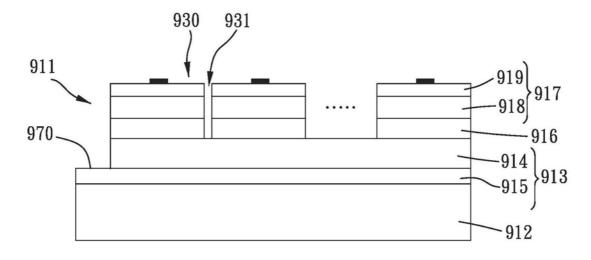

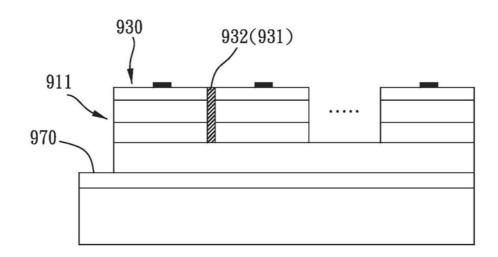

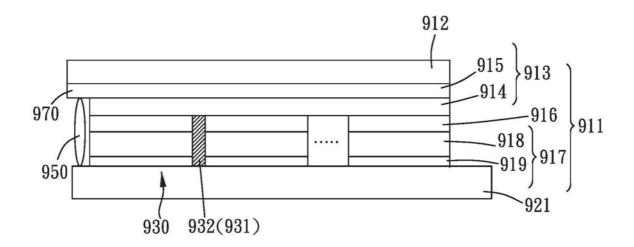

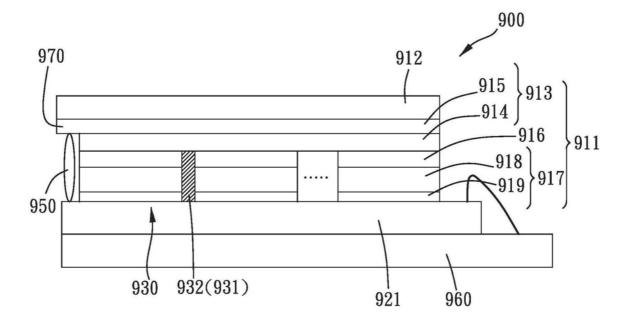

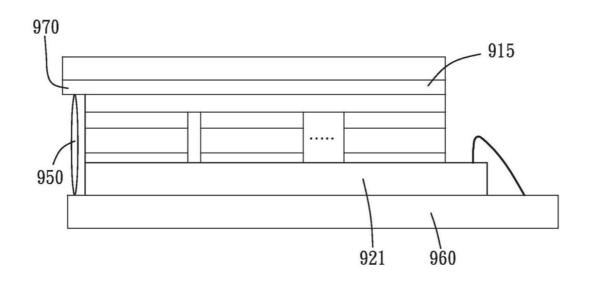

[0100] 请参阅图9A、9B、9E、9F、9G,其显示本发明的第四实施例,本实施例的微发光二极管显示模块900的制造方法包括以下步骤。

[0101] 一开始,制备一发光二极管晶圆910及一驱动电路晶圆920。该发光二极管晶圆910的部分区域界定为一发光二极管区块911,该驱动电路晶圆920的一芯片大小的区域界定为一驱动芯片区块921,其中该发光二极管区块911具有一第一半导体层、一发光层916、及一第二半导体层,该发光层916设于该第一半导体层及该第二半导体层之间,该第一半导体层连接一蓝宝石基材912,该第一及该第二半导体层其中一者系为N型半导体层、另一者系为P型半导体层。更明确地说,该第一半导体层系为N型半导体层913,该第二半导体层系为P型半导体层917。其中,该N型半导体层913包括一N型掺杂层914及一N型缓冲层915,该N型掺杂层914位于该N型缓冲层915与该发光层916之间。该P型半导体层917还包括一P型掺杂层918及一P型缓冲层919,该P型掺杂层918位于该P型缓冲层919与该发光层916之间,于某些实施例,亦可不具有N型或P型缓冲层。

[0102] 请参阅图9A,蚀刻该发光二极管区块911,而形成交错排列的多个沟槽931,该等沟槽931界定出呈矩阵排列的多个微发光二极管像素930,各该沟槽931穿透该P型半导体层917及该发光层916。进一步说,各该沟槽931未穿透该N型半导体层913,该N型半导体层913具有对应该等微发光二极管像素930的共同电极。于另一实施例,亦可以使各该沟槽穿透该N型掺杂层,只要至少部分该N型半导体层可作为共同电极即可。可理解的是,于进行蚀刻该发光二极管区块的步骤时,可以系蚀刻整个发光二极管晶圆、抑或是仅蚀刻经过切割分离的发光二极管区块911。并且,该N型半导体层913具有对应该等微发光二极管像素930的共同电极,且该共同电极水平方向上凸伸有一凸出部970,于本实施例,该N型缓冲层915具有该凸出部970,该凸出部970系于执行蚀刻发光二极管步骤中产生的,而该N型缓冲层915系为该等为发光二极管像素的共同电极。

[0103] 接着,请参阅图9B,将非导电胶932注入该等沟槽931,以增加该等微发光二极管像素930之间的结构强度。于某些实施例中,亦可不进行此步骤。

[0104] 接着,请参阅图9E及9F,接合该发光二极管区块911及该驱动芯片区块921,其中该P型半导体层917电性连接该驱动芯片区块921的多个像素电极。较佳地,为避免影响材料性质,该发光二极管块与该驱动芯片区块921系以低于摄氏200度的低温混合连接技术进行接

合。且各该微发光二极管像素930对应一该像素电极。如此一来,即可透过各该像素电极单独供电给相对应的微发光二极管像素930。要说明的是,各该微发光二极管像素930通常尺寸系微米级。要说明的是,于本实施例,该发光二极管区块911及该驱动芯片区块921系为已分别从该发光二极管晶圆及该驱动电路晶圆切割分离的区块,之后才进行此接合步骤。可理解的是,于其它实施例,如图9C,亦可将整个发光二极管晶圆910与驱动电路晶圆920接合;抑或是,如图9D,先从该发光二极管晶圆切割分离出该发光二极管区块911,再将该发光二极管区块911接合至该驱动电路晶圆920中像对应的位置上,之后再进行切割。

[0105] 除此之外,该凸出部970藉由一导电胶950电性连接该驱动芯片区块921,透过该N型缓冲层915与该等像素电极之间的电位差,即可控制各该微发光二极管像素930发亮。

[0106] 要说明的是,此实施例毋须将该蓝宝石基材912去除。

[0107] 接下来,请参阅图9G,将该驱动芯片区块921另与一电路板960电性连接,要说明的是,进行此步骤时,该驱动芯片区块921与该发光二极管区块911皆系已从该驱动电路晶圆及该发光二极管晶圆上切割分离的区块(即为独立的发光二极管像素阵列以及驱动芯片)。于另一实施例,例如图9H,导电胶950亦可不连接该驱动芯片区块921,而系连接该凸出部970与该电路板960。于某些实施例中,亦可不设有导电胶950,而将该IT0导电膜以其它导体电性连接其它外部电源,只要IT0导电膜与像素电极之间具有电位差即可,即可使各该微发光二极管像素930发亮。

[0108] 本实施例经过上述步骤,即制造出如图9G所示的微发光二极管显示模块。该微发光二极管显示模块包括该驱动芯片区块921、该发光二极管区块911、及该电路板960。该驱动芯片区块921具有该多个像素电极。该发光二极管区块911设于该驱动芯片区块921上。该发光二极管区块911具有该第一半导体层、该发光层916、该第二半导体层、及该多个沟槽931。该发光层916位于该第一及该第二半导体层之间,该第二半导体层电性连接该等像素电极,该等沟槽931界定出该多个呈矩阵排列的微发光二极管像素930,各该沟槽931穿透该第二半导体层及该发光层916。各该微发光二极管像素930对应一该像素电极。各该沟槽931穿透该第二半导体层及该发光层916。各该微发光二极管像素930对应一该像素电极。各该沟槽931内填充有非导电胶932。该第一半导体层水平方向上凸伸有该凸出部970。且该第一半导体层与该蓝宝石基材912相连接,该第一半导体层介于该蓝宝石基材912与该发光层916之间。[0109] 该电路板960之间,该点出部970与该驱动芯片区块921之间没有一层电路

极管区块911与该电路板960之间。该凸出部970与该驱动芯片区块921之间设有一导电胶950,该导电胶950分别电性连接该凸出部970及该驱动芯片区块921。于另一实施例,如图9H所示,亦可将导电胶950设于该凸出部970与该电路板960之间,该导电胶950分别电性连接该凸出部970及该电路板960。

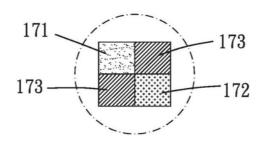

[0110] 请参阅图10,为了使上述所有实施例的微发光二极管显示模块发出不同颜色,可另外设置一色层170(RGB色层),以使该微发光二极管显示模块发出三色光。进一步说,该色层170的形成方式系于各该微发光二极管像素上方喷涂相对应的RGB量子点,以各该微发光二极管像素的发光激发量子点产生三色光。进一步说,该色层170具有多个红色、蓝色、绿色的像素区域171、172、173,各该像素区域171、172、173对应一该微发光二极管像素,而该色层170具有多个全色显示点(可显示三色光的最小单位)。各该全色显示点具有至少三个相邻的像素区域171、172、173,各该全色显示点至少包括一该红色像素区域171、一该蓝色像素区172域以及一该绿色像素区域173。较佳地,为了制程需求,一该全色显示点可包括四个

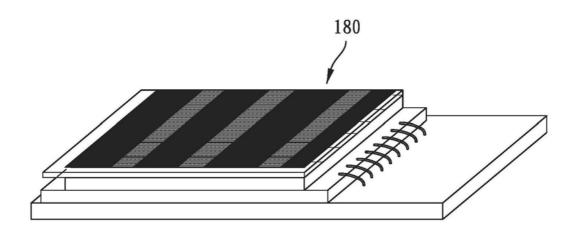

相邻的像素区域(例如一个红色像素区域171、一个蓝色像素区域172及二个绿色像素区域173),以使全色显示点的排列较有规律。于其它实施例,如图11所示,色层180亦可为RGB滤光片。

图4

图5

图6A

图6B

图6C

图6D

图6E

图6F

图6G

图6H

20

图6I

图7A

图7B

图7C

图7D

图7E

图7F

图7G

图7H

图7I

图7J

图7K

图7L

图8A

图8B

图8C

图8D

图8E

图8F

图8G

图9A

图9B

图9C

图9D

图9E

图9F

图9G

图9H

图10A

图10

图11

| 专利名称(译)        | 微发光二极管显示模块及其制造方法         |         |            |  |

|----------------|--------------------------|---------|------------|--|

| 公开(公告)号        | CN109037260A             | 公开(公告)日 | 2018-12-18 |  |

| 申请号            | CN201710431792.1         | 申请日     | 2017-06-09 |  |

| [标]申请(专利权)人(译) | 美商晶典有限公司                 |         |            |  |

| 申请(专利权)人(译)    | 美商晶典有限公司                 |         |            |  |

| 当前申请(专利权)人(译)  | 美商晶典有限公司                 |         |            |  |

| [标]发明人         | 黄振潮<br>王协友<br>吕旻晃<br>王利明 |         |            |  |

| 发明人            | 黄振潮<br>王协友<br>吕旻晃<br>王利明 |         |            |  |

| IPC分类号         | H01L27/15                |         |            |  |

| CPC分类号         | H01L27/15                |         |            |  |

| 代理人(译)         | 徐伟                       |         |            |  |

| 外部链接           | Espacenet SIPO           |         |            |  |

### 摘要(译)

本发明关于一种微发光二极管显示模块及其制造方法。该微发光二极管显示模块,包括一驱动芯片区块、一发光二极管区块、一电路板及一色层。该驱动芯片区块具有多个像素电极。该发光二极管区块设于该驱动芯片区块,且具有二半导体层、及多个沟槽,该二半导体层其中一者电性连接该等像素电极、另一者连接一透光导电层。该等沟槽界定出多个呈矩阵排列的微发光二极管像素,各该沟槽至少穿透该发光层、及一该半导体层,各该微发光二极管像素对应一该像素电极。该电路板电性连接该驱动芯片区块,该色层设于该透光导电层。